# **Datasheet ADQ8-4X**

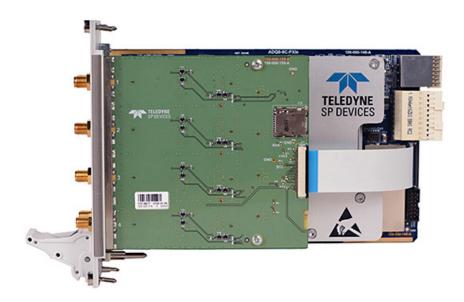

ADQ8-4X is a digitizer for modular instrumentation.

ADQ8-4X is intended for large scale integration and features:

10 bits vertical resolution

4 and 2 analog channels

2 and 4 GSPS per channel

Multi-unit synchronization for large installations

Open FPGA for custom real-time applications (option)

## **ADQ8-4X Datasheet**

#### **Features**

- 4 / 2 analog channels

- 2 / 4 GSPS sample rate per channel

- 10 bits vertical resolution

- Input impedance 50  $\Omega$

- DC-coupled

- 1 GHz analog bandwidth

- · Digital filter for bandwidth control

- Programmable DC-offset

- High sensitivity input

- Vertical range setting 0.25 Vpp to 5 Vpp

- Over-voltage protection

- · Internal clock reference

- Backplane clock reference

- · Trigger time interpolation

- · External trigger

- Multi-unit synchronization

- Timestamp for real-time operation

- 1 GBytes data memory

- 2.6 GBytes/s data streaming

- Available in PXIe form factor

- Digitizer Studio application software included

- Daisy chain multi-channel synchronization

### **Applications**

- · Ultrasound applications

- Non-destructive testing

- · Wireless communication

- Time-of-flight

- Scientific instruments

- · Particle physics

- Thomson scattering

- Semiconductor test

- ATE

- Test and measurement

- Quantum technology

### **Advantages**

- Host PC interface options and large scale integration support for optimized systems partitioning.

- Advanced analog front-end and high sample rate for meeting detector and measurement requirements.

- Application specific firmware options and realtime custom processing solutions for advanced systems for optimized cost of ownership.

- SP Devices' design services are available for fast integration to lower the time-to-market.

## **Options summary**

| ORDER CODE            | NAME                               | DESCRIPTION                                                                      |

|-----------------------|------------------------------------|----------------------------------------------------------------------------------|

| -VG <sup>1</sup>      | Full flexible analog front-<br>end | Flexible analog front-end including user controlled DC-offset, and voltage range |

| –PXIE                 | PXI Express format                 | Form factor for integration in a PXI Express 3U chassis                          |

| -MTCA <sup>2</sup>    | MTCA.4 format                      | Form factor for integration in a MTCA.4 chassis.                                 |

| -FWDAQ2G <sup>3</sup> | Data acquisition firmware          | Data acquisition functions for 4 channels, 2 GSPS                                |

| -FWDAQ4G <sup>4</sup> | Data acquisition firmware          | Data acquisition functions for 2 channels, 4GSPS                                 |

| -DEV8DAQ <sup>5</sup> | Firmware development kit           | Open the FPGA to add custom firmware to  –FWDAQ2G and –FWDAQ4G                   |

- 1. Always included with the ADQ8-4X. Availability of ADQ8-4X without –VG option installed is to be confirmed. Please contact a TSPD sales representative for more information.

- 2. Availability is to be confirmed. Please contact a TSPD sales representative for more information.

- 3. Always included with the ADQ8-4X.

- 4. Always included with the ADQ8-4X.

- 5. Purchased separately. Development kit for -FWDAQ2G and -FWDAQ4G included.

### 1 Technical data

All values are typical unless otherwise noted.

All parameters are valid for and limited to firmware –FWDAQ2G unless otherwise noted.

Table 1: Analog input with –VG option installed. Typical parameters.

| PARAMETER                                 |               | -VG-FWDAQ2G   | -VG-FWDAQ4G        |

|-------------------------------------------|---------------|---------------|--------------------|

| Analog inputs                             |               |               |                    |

| Connector                                 |               | SI            | МA                 |

| Coupling                                  |               | C             | C                  |

| Input range settings                      | $[V_{pp}]$    | -             | 25                 |

|                                           |               | -             | .5                 |

|                                           |               |               | 1<br>.5            |

|                                           |               |               | 5                  |

| Variable DC-offset                        | [V]           | ± 0.5 *       | range <sup>1</sup> |

| Cross talk isolation DC – 500 MHz         | [MHz]         | > 60          | ) dB               |

| Over-voltage protection                   |               | See Ta        | able 11            |

| Input impedance                           | [Ω]           | 50 ±          | : 3 %              |

| Idle channel noise (Range 0.25)           | [dBFS / Hz]   | <b>–135.8</b> | -138.8             |

| Idle channel noise (Range 0.5 1 2.5 5)    | [dBFS / Hz]   | <b>–141.8</b> | -144.8             |

| Flatness –1 dB                            | [MHz]         | 300           | 300                |

| Bandwidth upper limit –3 dB               | [MHz]         | 1000          | 1000               |

| Analog performance. Test signal at -1     | dBFS up to 40 | 2 MHz.        |                    |

| SNR (Range 0.25 V <sub>pp</sub> )         | [dBFS]        | 46            | 46                 |

| SNR (Range 0.5 1 2.5 5 V <sub>pp</sub> )  | [dBFS]        | 51            | 51                 |

| SFDR <sup>2</sup> (All ranges)            | [dBFS]        | 64            | 64                 |

| SFDR <sup>3</sup> (All ranges)            | [dBFS]        | _             | 57                 |

| ENOB (Range 0.25 V <sub>pp</sub> )        | [bits]        | 7.4           | 7.4                |

| ENOB (Range 0.5 1 2.5 5 V <sub>pp</sub> ) | [bits]        | 8.0           | 8.0                |

<sup>1.</sup> Rail-to-rail on all input range settings.

<sup>2.</sup> Not including Interleaving tone

<sup>3.</sup> Interleaving tone included

Table 2: Clock

| PARAMETER                          |       | –FWDAQ2G                         | –FWDAQ4G                         |

|------------------------------------|-------|----------------------------------|----------------------------------|

| Internal Clock Reference           |       |                                  |                                  |

| Frequency                          | [MHz] | 10 ± 3 ppm                       | 10 ± 3 ppm                       |

| Drift                              |       | ± 1 ppm / year                   | ± 1 ppm / year                   |

| PXIe backplane clock reference     |       |                                  |                                  |

| PXIe sync                          | [MHz] | 10                               | 10                               |

| PXIe clock                         | [MHz] | 100                              | 100                              |

| Backplane clock reference accuracy |       | ± 10 ppm                         | ± 10 ppm                         |

| External clock reference           |       |                                  |                                  |

| Frequency                          | [MHz] | 10                               | 10                               |

| Clock reference output             |       |                                  |                                  |

| Frequency                          | [MHz] | 10                               | 10                               |

| External clock                     |       |                                  |                                  |

| Clock frequency                    | [MHz] | 1000 ( <sup>1</sup> )            | 1000 ( <sup>2</sup> )            |

| Sample skip                        |       |                                  |                                  |

| Ratio <sup>3</sup>                 |       | 1 2 4 8 10 12 14 2 <sup>16</sup> | 1 2 4 8 10 12 14 2 <sup>16</sup> |

| Front panel connector clock input  |       |                                  |                                  |

| Signal level minimum               | [Vpp] | 0.2                              | 0.2                              |

| Signal level recommended           | [Vpp] | 0.6                              | 0.6                              |

| Signal level maximum               | [Vpp] | 0.8                              | 0.8                              |

| Input impedance AC                 | [Ω]   | 50                               | 50                               |

| Input impedance DC                 | [Ω]   | 10 k                             | 10 k                             |

| Connector                          |       | SMA                              | SMA <sup>4</sup>                 |

| Front panel connector clock output |       |                                  |                                  |

| Level (into 50 $\Omega$ , typical) | [V]   | 1.6                              | 1.6                              |

| Output impedance AC                | [Ω]   | 50                               | 50                               |

| Output impedance DC                | [Ω]   | 10 k                             | 10 k                             |

| Coupling                           |       | AC                               | AC                               |

| Connector                          |       | MCX                              | MCX                              |

- 1. The external clock frequency of 1 GHz result in a sampling rate of 2 GSPS.

- The external clock frequency of 1 GHz result in a sampling rate of 4 GSPS.

Sample skip ratio of 200 means that the data rate is reduced a factor of 200, that is from 1 GSPS to 5 MSPS.

- 4. Connector is shared between input and output. The direction is software controlled.

Table 3: Trigger

| PARAMETER                                                     |            | ADQ8-4X–VG–PXIE |  |  |

|---------------------------------------------------------------|------------|-----------------|--|--|

| Analog channel as trigger <sup>1</sup>                        |            |                 |  |  |

| Connector                                                     |            | SMA             |  |  |

| Impedance DC                                                  | $[\Omega]$ | see Table 1     |  |  |

| Signal level <sup>2</sup>                                     | [V]        | see Table 1     |  |  |

| Signal swing                                                  | [Vpp]      | see Table 1     |  |  |

| Adjustable software controlled trigger threshold <sup>3</sup> | [V]        | see Table 1     |  |  |

| Time resolution (interpolated value)                          | [ps]       | 25              |  |  |

| Jitter RMS                                                    | [ps]       | 10              |  |  |

| Star B backplane trigger                                      |            |                 |  |  |

| Connector                                                     |            | Backplane       |  |  |

| Time resolution                                               | [ns]       | 4               |  |  |

| External trigger input on front panel                         |            |                 |  |  |

| Connector (shared with output)                                |            | SMA             |  |  |

| Time resolution                                               | [ns]       | 1               |  |  |

| Adjustable threshold                                          | [V]        | 0 to +3.0       |  |  |

| Signal level                                                  | [V]        | -0.5 to +3.3    |  |  |

| Input impedance                                               | $[\Omega]$ | 50              |  |  |

| Input impedance high <sup>4</sup>                             | [Ω]        | 500             |  |  |

| External trigger output on front panel                        |            |                 |  |  |

| Connector (shared with input)                                 |            | SMA             |  |  |

| Level (no load, typical)                                      | [V]        | 0 to +3.3       |  |  |

| Output impedance                                              | [Ω]        | 50              |  |  |

- 1. Use one of the analog inputs as trigger. The timing of the trigger is interpolated to high accuracy.

- 2. Use the DC-offset and range settings to adjust to the trigger signal. See Table 1 for details.

- 3. The setting of the threshold is within the signal range selected.

- 4. Software controlled high impedance for bussed connection.

Table 4: SYNC trigger signal

|                                     |      | ADQ8-4X-VG-PXIE |

|-------------------------------------|------|-----------------|

| Output                              |      |                 |

| Connector                           |      | MCX             |

| Impedance DC                        | [Ω]  | 50              |

| Signal level output (no load)       | [V]  | 0 to 3.3        |

| Input                               |      |                 |

| Connector                           |      | MCX             |

| Impedance DC <sup>1</sup>           | [Ω]  | 10 k            |

| Vil_max                             | [V]  | 0.8             |

| Vih_min                             | [V]  | 2.0             |

| Input synchronous mode <sup>2</sup> |      |                 |

| Time resolution                     | [ns] | 100             |

| Input asynchronous mode             |      |                 |

| Time resolution                     | [ns] | 4               |

| Jitter asynchronous mode RMS        | [ns] | 1.15            |

- 1. The signal has to be source terminated with 50  $\Omega.\,$

- 2. Synchronous mode phase locked to 10 MHz reference.

Table 5: General specifications

|                                                                 |         | ADQ8-4X-VG-PXIE                                             |

|-----------------------------------------------------------------|---------|-------------------------------------------------------------|

| Key parameters                                                  | '       |                                                             |

| Channels (–FWDAQ2G)                                             |         | 4                                                           |

| Sample rate / channel (–FWDAQ2G)                                | [GSPS]  | 2                                                           |

| Channels (–FWDAQ4G)                                             |         | 2                                                           |

| Sample rate / channel (–FWDAQ4G)                                | [GSPS]  | 4                                                           |

| Resolution                                                      | [bits]  | 10                                                          |

| Data memory <sup>1</sup>                                        | [GByte] | 1                                                           |

| Firmware function                                               | ·       |                                                             |

| Trigger modes                                                   |         | Channel, External, Backplane Star B, Software               |

| Clock reference                                                 |         | Internal, External, Backplane                               |

| Acquisition modes                                               |         | Multi-record, Triggered streaming                           |

| Synchronization Daisy-chain trigger, trigger time interpolation |         | Daisy-chain trigger, trigger time interpolation             |

| Mechanical                                                      |         |                                                             |

| Weight                                                          | [g]     | 520                                                         |

| Board width including –VG                                       | [slot]  | 2                                                           |

| Board height                                                    |         | 3U                                                          |

| Electrical                                                      |         |                                                             |

| Power supply                                                    | [V]     | 12                                                          |

| Power dissipation                                               | [W]     | 46                                                          |

| Temperature range                                               |         |                                                             |

| Ambient operating                                               | [°C]    | 0 to 45 <sup>2</sup>                                        |

| Storage                                                         |         |                                                             |

| Compliances                                                     |         |                                                             |

| CE                                                              |         | ✓                                                           |

| RoHS3                                                           |         | ✓                                                           |

| FCC                                                             |         | Exclusion according to CFR 47, part 15, paragraph 15.103(c) |

- 1. The data memory is shared between data from all channels.

- 2. High fan setting required if available on the chassis. Blocking airflow through empty slots is recommended and may be necessary.

Table 6: Data acquisition parameters -FWDAQ2G: Multi-record

|                               |                       | STEP SIZE | MIN / MAX               |

|-------------------------------|-----------------------|-----------|-------------------------|

| Rearm time                    | [us]                  | -         | 4                       |

| Pre-trigger length            | [samples]             | 1         | 0 to record length      |

| Trigger delay                 | [samples]             | 8         | 0 to 2 <sup>32</sup> –8 |

| Record length                 | [samples]             | 1         | 8 to 100 M              |

| Data transfer speed max       | [GBytes/s]            | _         | 3.2                     |

| Data transfer speed sustained | [GSamples/s]          | _         | 1.3                     |

| Data memory                   | [samples per channel] | _         | 100 M                   |

Table 7: Data acquisition parameters –FWDAQ2G: Triggered streaming.

|                               |                       | STEP SIZE | MIN / MAX               |

|-------------------------------|-----------------------|-----------|-------------------------|

| Rearm time                    | [ns]                  | -         | max 168                 |

| Pre-trigger length            | [samples]             | 8         | 0 to 16 k               |

| Trigger delay                 | [samples]             | 8         | 0 to 2 <sup>32</sup> –8 |

| Record length                 | [samples]             | 8         | 8 to 100 M              |

| Data transfer speed max       | [GBytes/s]            | -         | 3.2                     |

| Data transfer speed sustained | [GSamples/s]          | -         | 1.3                     |

| Data memory                   | [samples per channel] | -         | 100 M                   |

Table 8: Data acquisition parameters -FWDAQ4G: Multi-record

|                               |                       | STEP SIZE | MIN / MAX                |

|-------------------------------|-----------------------|-----------|--------------------------|

| Rearm time                    | [us]                  | -         | 4                        |

| Pre-trigger length            | [samples]             | 1         | 0 to record length       |

| Trigger delay                 | [samples]             | 16        | 0 to 2 <sup>32</sup> –16 |

| Record length                 | [samples]             | 1         | 8 to 200 M               |

| Data transfer speed max       | [GBytes/s]            | -         | 3.2                      |

| Data transfer speed sustained | [GSamples/s]          | -         | 1.3                      |

| Data memory                   | [samples per channel] | _         | 100 M                    |

Table 9:

Data acquisition parameters –FWDAQ4G: Triggered streaming.

|                               |                       | STEP SIZE | MIN / MAX                |

|-------------------------------|-----------------------|-----------|--------------------------|

| Rearm time                    | [ns]                  | -         | max 168                  |

| Pre-trigger length            | [samples]             | 16        | 0 to 16 k                |

| Trigger delay                 | [samples]             | 16        | 0 to 2 <sup>32</sup> –16 |

| Record length                 | [samples]             | 16        | 8 to 200 M               |

| Data transfer speed max       | [GBytes/s]            | -         | 3.2                      |

| Data transfer speed sustained | [GSamples/s]          | -         | 1.3                      |

| Data memory                   | [samples per channel] | -         | 100 M                    |

**Table 10: Software support**

|                                    | COMMENT         |  |  |  |

|------------------------------------|-----------------|--|--|--|

| Operating systems <sup>1</sup>     |                 |  |  |  |

| Windows 8 / 8.1, 32-bit and 64-bit | ✓               |  |  |  |

| Windows 10, 32-bit and 64-bit      | ✓               |  |  |  |

| Linux                              | ✓               |  |  |  |

| Application                        |                 |  |  |  |

| C/C++                              | API, examples   |  |  |  |

| Python                             | Example scripts |  |  |  |

| Digitizer Studio Application tool  |                 |  |  |  |

<sup>1.</sup> See "15-1494 Operating System Support" for supported distributions.

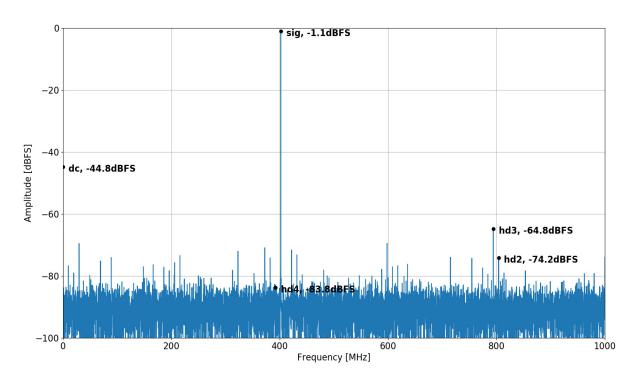

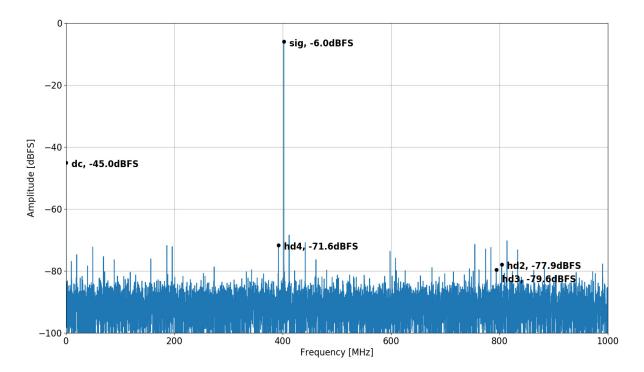

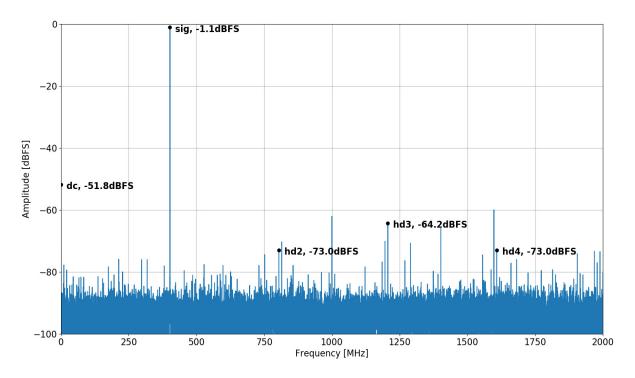

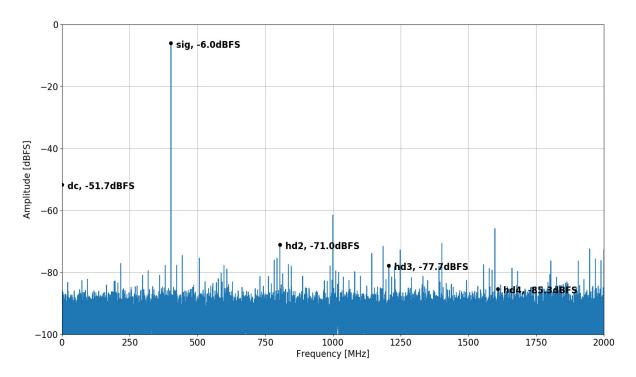

# 2 Spectral response

Figure 1: ADQ8-4X-VG-FWDAQ2G spectral performance at -1 dBFS, range 0.5 Vpp.

Figure 2: ADQ8-4X-VG-PXIE spectral performance at -6 dBFS, range 0.5 Vpp.

Figure 3: ADQ8-4X-VG-FWDAQ4G spectral performance at -1 dBFS, range 0.5 Vpp.

Figure 4: ADQ8-4X-VG-FWDAQ4G spectral performance at -6 dBFS, range 0.5 Vpp.

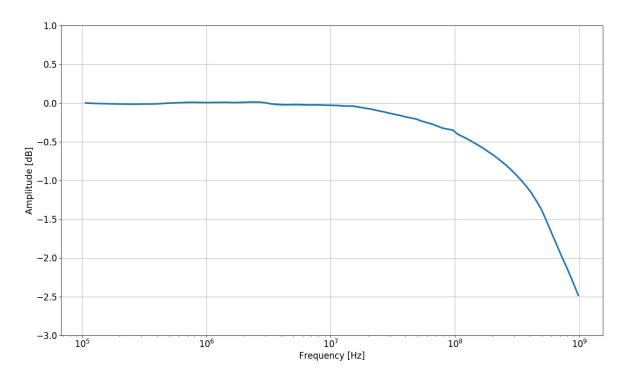

## 3 Frequency response

Figure 5: ADQ8-4X-VG, -FWDAQ2G and -FWDAQ4G frequency response.

## 4 Absolute maximum ratings

Stresses beyond conditions listed under Absolute Maximum Ratings **Table 11** may cause permanent damage to the device. The analog inputs are protected from over-voltage but the values in **Table 11** must never be exceeded.

Built-in temperature monitoring protects the ADQ8-4X from overheating shutting down parts of the device in an overheat situation.

**Table 11: Absolute Maximum Ratings**

| PARAMETER                 |      | MIN          | MAX   |

|---------------------------|------|--------------|-------|

| Analog input <sup>1</sup> |      |              |       |

| Voltage to GND            | [V]  | <b>–</b> 5.0 | + 5.0 |

| Trigger                   |      |              |       |

| Voltage to GND            | [V]  | -2.3         | 5.0   |

| SYNC                      |      |              |       |

| Voltage to GND            | [V]  | -0.3         | +3.6  |

| CLKIN                     |      |              |       |

| Voltage to GND            | [V]  | <b>-</b> 5.0 | +5.0  |

| Power supply              |      |              |       |

| Voltage to GND            | [V]  | -0.4         | 14    |

| Temperature               |      |              |       |

| Ambient operating         | [°C] | 0            | 45    |

<sup>1.</sup> Also valid for analog channel used as trigger.

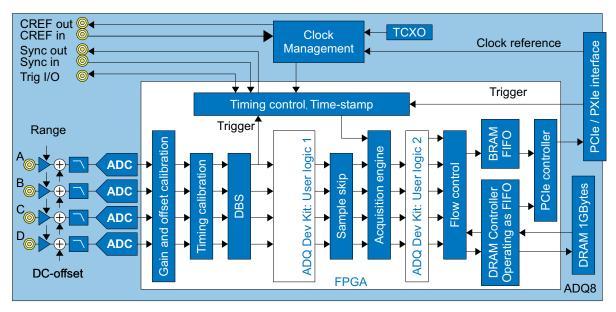

### 5 Block diagram

Figure 6: Block diagram for ADQ8-4X

### **Important Information**

Teledyne Signal Processing Devices Sweden AB (Teledyne SP Devices) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to Teledyne SP Devices' general terms and conditions supplied at the time of order acknowledgment.

Teledyne SP Devices warrants that each product will be free of defects in materials and workmanship, and conform to specifications set forth in published data sheets, for a period of three (3) years. The warranty commences on the date the product is shipped by Teledyne SP Devices. Teledyne SP Devices' sole liability and responsibility under this warranty is to repair or replace any product which is returned to it by Buyer and which Teledyne SP Devices determines does not conform to the warranty. Product returned to Teledyne SP Devices for warranty service will be shipped to Teledyne SP Devices at Buyer's expense and will be returned to Buyer at Teledyne SP Devices' expense. Teledyne SP Devices will have no obligation under this warranty for any products which (i) has been improperly installed; (ii) has been used other than as recommended in Teledyne SP Devices' installation or operation instructions or specifications; or (iii) has been repaired, altered or modified by entities other than Teledyne SP Devices. The warranty of replacement products shall terminate with the warranty of the product. Buyer shall not return any products for any reason without the prior written authorization of Teledyne SP Devices.

In no event shall Teledyne SP Devices be liable for any damages arising out of or related to this document or the information contained in it.

TELEDYNE SP DEVICES' EXPRESS WARRANTY TO BUYER CONSTITUTES TELEDYNE SP DEVICES' SOLE LIABILITY AND THE BUYER'S SOLE REMEDY WITH RESPECT TO THE PRODUCTS AND IS IN LIEU OF ALL OTHER WARRANTIES, LIABILITIES AND REMEDIES. EXCEPT AS THUS PROVIDED, TELEDYNE SP DEVICES DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT.

TELEDYNE SP DEVICES DOES NOT INDEMNIFY, NOR HOLD THE BUYER HARMLESS, AGAINST ANY LIABILITIES, LOSSES, DAMAGES AND EXPENSES (INCLUDING ATTORNEY'S FEES) RELATING TO ANY CLAIMS WHATSOEVER. IN NO EVENT SHALL TELEDYNE SP DEVICES BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, INCLUDING LOST PROFIT, LOST DATA AND THE LIKE, DUE TO ANY CAUSE WHATSOEVER. NO SUIT OR ACTION SHALL BE BROUGHT AGAINST TELEDYNE SP DEVICES MORE THAN ONE YEAR AFTER THE RELATED CAUSE OF ACTION HAS ACCRUED. IN NO EVENT SHALL THE ACCRUED TOTAL LIABILITY OF TELEDYNE SP DEVICES FROM ANY LAWSUIT, CLAIM, WARRANTY OR INDEMNITY EXCEED THE AGGREGATE SUM PAID TO SP BY BUYER UNDER THE ORDER THAT GIVES RISE TO SUCH LAWSUIT, CLAIM, WARRANTY OR INDEMNITY.

### **Worldwide Sales and Technical Support**

www.spdevices.com

#### **Teledyne SP Devices Corporate Headquarters**

Teknikringen 6 SE-583 30 Linköping Sweden

Phone: +46 (0)13 465 0600 Fax: +46 (0)13 991 3044 Email: info@spdevices.com

Copyright © 2020 Teledyne Signal Processing Devices Sweden AB. All rights reserved, including those to reproduce this publication or parts thereof in any form without permission in writing from Teledyne SP Devices.